# Worcester Polytechnic Institute **Digital WPI**

Masters Theses (All Theses, All Years)

**Electronic Theses and Dissertations**

2017-04-27

# Side-Channel Attacks on Intel SGX: How SGX Amplifies The Power of Cache Attack

Ahmad Moghimi Worcester Polytechnic Institute

Follow this and additional works at: https://digitalcommons.wpi.edu/etd-theses

#### Repository Citation

Moghimi, Ahmad, "Side-Channel Attacks on Intel SGX: How SGX Amplifies The Power of Cache Attack" (2017). Masters Theses (All Theses, All Years). 399.

https://digitalcommons.wpi.edu/etd-theses/399

This thesis is brought to you for free and open access by Digital WPI. It has been accepted for inclusion in Masters Theses (All Theses, All Years) by an authorized administrator of Digital WPI. For more information, please contact wpi-etd@wpi.edu.

# Side-Channel Attacks on Intel SGX: How SGX Amplifies The Power of Cache Attacks

by

Ahmad Moghimi

A Thesis

Submitted to the Faculty

of the

#### WORCESTER POLYTECHNIC INSTITUTE

In partial fulfillment of the requirements for the

Degree of Master of Science

in

Computer Science

by

|                                                   | April 27, 2017 |  |  |

|---------------------------------------------------|----------------|--|--|

| APPROVED:                                         |                |  |  |

|                                                   |                |  |  |

| Professor Thomas Eisenbarth, Major Thesis Advisor |                |  |  |

| Professor Robert Walls, Thesis Reader             |                |  |  |

Professor Craig E. Wills, Head of Department

#### Abstract

In modern computing environments, hardware resources are commonly shared, and parallel computation is more widely used. Users run their services in parallel on the same hardware and process information with different confidentiality levels every day. Running parallel tasks can cause privacy and security problems if proper isolation is not enforced. Computers need to rely on a trusted root to protect the data from malicious entities. Intel proposed the Software Guard eXtension (SGX) to create a trusted execution environment (TEE) within the processor. SGX allows developers to benefit from the hardware level isolation.

SGX relies only on the hardware, and claims runtime protection even if the OS and other software components are malicious. However, SGX disregards any kind of side-channel attacks. Researchers have demonstrated that microarchitectural side-channels are very effective in thwarting the hardware provided isolation. In scenarios that involve SGX as part of their defense mechanism, system adversaries become important threats, and they are capable of initiating these attacks.

This work introduces a new and more powerful cache side-channel attack that provides system adversaries a high resolution channel. The developed attack is able to virtually track all memory accesses of SGX execution with temporal precision. As a proof of concept, we demonstrate our attack to recover cryptographic AES keys from the commonly used implementations including those that were believed to be resistant in previous attack scenarios. Our results show that SGX cannot protect critical data sensitive computations, and efficient AES key recovery is possible in a practical environment. In contrast to previous attacks which require hundreds of measurements, this is the first cache side-channel attack on a real system that can recover AES keys with a minimal number of measurements. We can successfully recover the AES key from T-Table based implementations in a known plaintext and ciphertext scenario with an average of 15 and 7 samples respectively.

#### Acknowledgements

I would like to express my deepest acknowledgement to my advisor, Prof. Thomas Eisenbarth, for his professional tutoring and close collaboration during this research project. His support during every step of this work made this master thesis less challenging and more enjoyable. It was a great experience, and I am honored to continue to work with him.

I also want to thank my thesis reader, Prof. Robert Walls, for his time and attention and notable comments on the authorship of this work. I would like to thank my department head, Prof. Craig Wills, for his support on pursing this valuable degree.

I would like to give my kindest regards to Gorka Irazoqui Apecechea, Joshua Pritchett, Curtis Taylor, Hang Cai, Amit Srivastava, Berk Gulmezoglu, Mehmet Sinan Inci, Mohammad Essedik Najd and Okan Seker for creating a friendly and joyful environment here in WPI.

I would like to thank my father Mohammad-Hassan, my mother Zahra, my brother Amir and my sister Maryam. They have always supported me throughout the course of life. At the end, thank you to Nathalie Majcherczyk, for all of her love and support.

Part of this work are currently under submission at a peer-review venue, with a preprint available as *CacheZoom* [42].

# Contents

| 1        | Intr | roduction                                    | 7        |

|----------|------|----------------------------------------------|----------|

|          | 1.1  | Motivation                                   | 7        |

|          | 1.2  | Contribution                                 |          |

|          | 1.3  | Outline of the work                          |          |

| <b>2</b> | Bac  | kground & Related Work                       | 10       |

|          | 2.1  | Intel SGX                                    | 10       |

|          |      | 2.1.1 Memory Encryption Engine (MEE)         | 11       |

|          | 2.2  | Cache Memory                                 |          |

|          |      | 2.2.1 Cache Addressing Schema                |          |

|          |      | 2.2.2 Cache Coherency and Replacement policy |          |

|          | 2.3  | Microarchitectural Attacks in SGX            | 15       |

|          |      | 2.3.1 Prime+Probe                            | 16       |

|          | 2.4  | Side-Channel Attacks & SGX                   |          |

| 3        | Cac  | the Side-Channel Attack on SGX               | 20       |

| _        | 3.1  | Attack Design                                |          |

|          |      | 3.1.1 Adversarial Model                      |          |

|          |      | 3.1.2 Cache Partitioning & Noise Reduction   |          |

|          |      | 3.1.3 Step by Step Execution                 |          |

|          |      | 3.1.4 Summary                                |          |

|          | 3.2  | Attack Implementation                        |          |

|          | 0    | 3.2.1 Eviction Set                           |          |

|          |      | 3.2.2 Noise Reducing Configuration           |          |

|          |      | 3.2.3 Malicious Kernel Driver                |          |

| 4        | ΛF   | S in Practice                                | 28       |

| 4        | 4.1  | T-Table Implementations                      |          |

|          | 4.1  | -                                            |          |

|          |      | Non-vulnerable Implementations               |          |

|          | 4.3  | Table Prefetching as a Countermeasure        | 30<br>31 |

|          | 4.4  | Susceptibility to Cache Attacks              | .51      |

| <b>5</b> | AES | S Key Recovery Attack               | 33 |

|----------|-----|-------------------------------------|----|

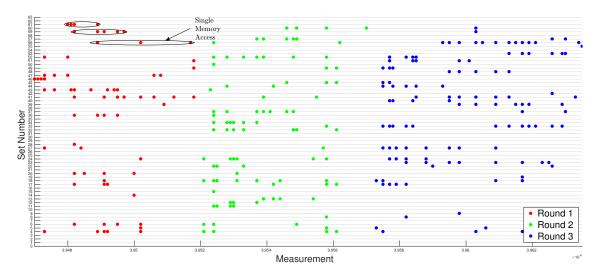

|          | 5.1 | Channel Measurement                 | 33 |

|          |     | 5.1.1 Experimental Setup            | 33 |

|          |     | 5.1.2 Eviction Set Quality          | 34 |

|          |     | 5.1.3 Channel Bandwidth             | 35 |

|          | 5.2 | AES T-Table KPA Attack              | 36 |

|          |     | 5.2.1 Cache Prefetching             | 39 |

|          | 5.3 | AES T-Table KCA Attack              | 40 |

|          |     | 5.3.1 Last Round Attack on T-Table  | 40 |

|          |     | 5.3.2 Last Round Attack Improvement | 41 |

|          | 5.4 | AES S-Box KCA Attack                | 43 |

| 6        | Con | aclusion                            | 47 |

# List of Figures

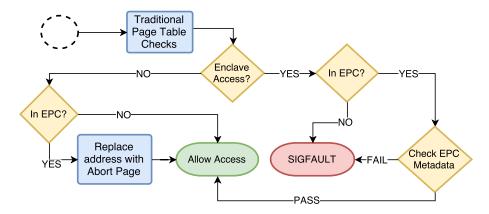

| 2.1  | Enclave Memory Access                                                | 11 |

|------|----------------------------------------------------------------------|----|

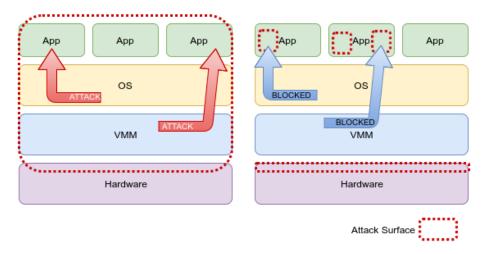

| 2.2  | Enclave Attack Surface                                               | 12 |

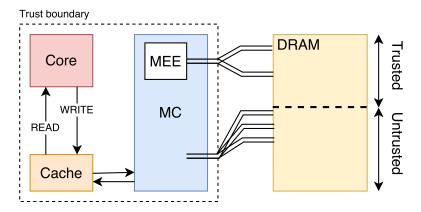

| 2.3  | MEE Operation                                                        |    |

| 2.4  | Memory hierarchy of a modern computer                                | 14 |

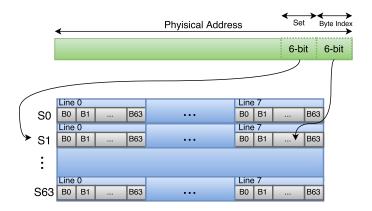

| 2.5  | L1D Cache Addressing Schema                                          | 15 |

| 3.1  | Isolated Core-private Channel                                        | 22 |

| 3.2  | Initialized pointers to chase                                        | 24 |

| 4.1  | Prime and Probe Prefetching Timeline                                 | 31 |

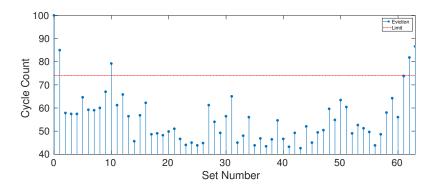

| 5.1  | Eviction cycle count                                                 | 34 |

| 5.2  | Average Eviction Noise                                               | 34 |

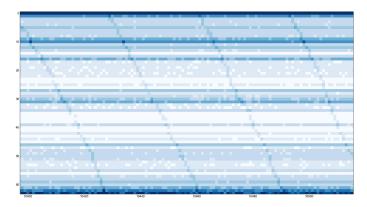

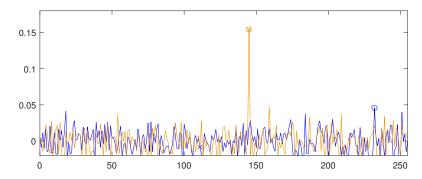

| 5.3  | Cache Hit Map                                                        | 35 |

| 5.4  | Cache Hit Map (Filtered)                                             | 35 |

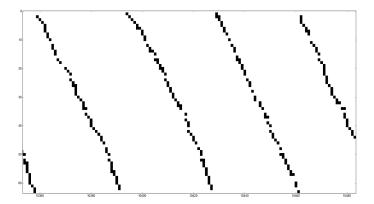

| 5.5  |                                                                      | 37 |

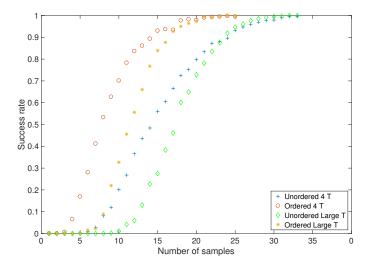

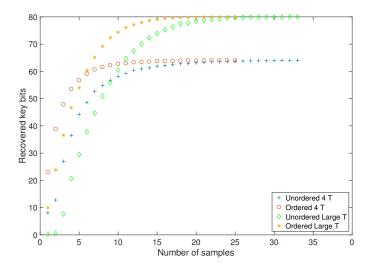

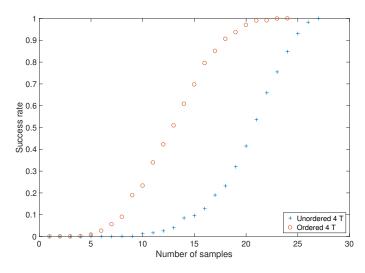

| 5.6  | First round attack key recovery success rate                         | 38 |

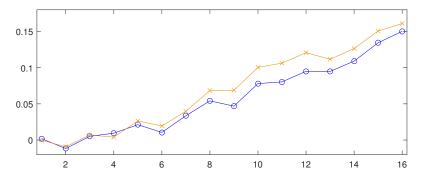

| 5.7  | First round attack correct recovered key bits                        | 39 |

| 5.8  |                                                                      | 40 |

| 5.9  |                                                                      | 41 |

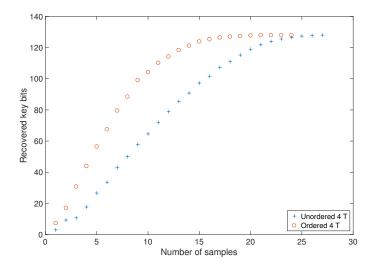

| 5.10 | Last round attack key recovery success rate                          | 42 |

| 5.11 | Correlation between observed cache accesses and predicted accesses . | 44 |

|      | Correlation over key value                                           | 45 |

# List of Tables

| 2.1 | Comparison of different side-channels against enclave                | 16 |

|-----|----------------------------------------------------------------------|----|

| 5.1 | Statistics on recovered memory accesses for T-table implementations. | 30 |

# Chapter 1

# Introduction

### 1.1 Motivation

In the world of parallel and distributed computing, processes with various trust and criticality levels are allowed to run at the same time and share system resources. Proliferation of cloud computing technology elevated these phenomena to the next level. Cloud computers running many different services authored by various providers process user information on the same physical hardware.

Traditionally, the operating system (OS) provides security services such as access control, encryption and authentication to isolate concurrent tasks from interfering with data and computation of other tasks. The dependence of various computation units i.e., threads, processes, etc. on a privileged root of trust realizes the concept of Trusted Computing Base (TCB) on the OS. In cloud computing, hypervisor software and cloud service providers also become part of the TCB. High complexity of modern computing and variety of attack surfaces make it unachievable to keep an entire system secure and trusted [37, 22].

Minimizing the size of TCB on the software is practically ineffective against attacks targeting the privileged mode of execution. There are numerous system services, drivers and kernel interfaces vulnerable to privilege escalation attacks. Third parties also contribute to this weakness by adding new features and extending the kernel size. One workaround is to outsource security-critical services to a Secure Element (SE) which is a separate hardware. Trusted Platform Modules (TPM), for example, provide services such as cryptography and secure boot beyond the authority of the OS [43].

Trusted Execution Environments (TEE) as an alternative to TPM attempt to provide similar services directly within the CPU. A TEE is an isolated environment to run software with a higher trust level than the OS. The software running inside a TEE has full access to the system resources while it is protected from other applications and from the OS. Examples include ARM TrustZone [3] and Intel Software Guard eXtension (SGX) [54]. Software solutions to virtualize or emulate TPM-like features on commodity hardware have been proposed. However, they suffer from

security and usability challenges [17, 30, 48, 58].

Intel SGX provides a TEE on an untrusted system by only trusting the hardware on which the code is executed. The runtime execution is secured inside an *enclave* which is encrypted and authenticated by the processor. In particular, the CPU decrypts and verifies the authenticity of an enclave code and data as it is moved into the processor cache. Enclaves are logically protected from the OS and malicious applications, and physical adversaries monitoring system buses. However, Intel SGX is not protected against attacks that utilize hardware resources as a covert channel [33]. And indeed, first works demonstrating that microarchitectural side channels can be exploited have been proposed, including attacks using page table faults [62], the branch prediction unit [38], and caches [51, 11].

Caches have become a very popular side channel in many scenarios, including mobile [39] and cloud environments [31]. More specifically, last level cache (LLC) attacks perform well in cross-core scenarios on Intel machines. Cache side channels provide an information leakage channel with the granularity of a cache line size. The small line size over the wide range of memory addresses has a high *spatial* resolution. This *spatial* resolution becomes very advantageous for the adversaries. For example, with a line size of only 64 bytes, attackers are able to distinguish accesses to different RSA multiplicands for windowed exponentiation algorithms [40]. This high spatial resolution, combined with a good temporal resolution, have enabled attacks on all major asymmetric cryptographic implementations.

For symmetric cryptography, the scenario is more challenging. An optimized table-based AES implementation can be executed in a few hundred cycles, while performing a single cache access time measurement on an LLC set is computationally more expensive. To avoid undersampling, synchronized attacks trigger a single encryption and perform one measurement, yielding at best one observation per encryption [7]. This heavily limits the observed information to perform key recovery attacks.

### 1.2 Contribution

Our study explores practicality of cache side-channel attacks on SGX. This increases the awareness of security community on an important threat affecting TEE platforms and in particular SGX. In addition, application of the attack on implementations of a cryptographic algorithm like AES shows that there exist weaknesses in the software. Some of these weaknesses can only be exploited in certain security scenarios.

In this work, we demonstrate not only that Intel SGX is vulnerable to cache based attacks, but also that the quality of information leakage channel is significantly high in the SGX environment. The resolution of our channel enables attacks that were infeasible in previously exploited scenarios, e.g., cloud environments or smartphones. In particular, we take advantage of the capabilities that SGX assumes an attacker has, i.e., access to the OS resources. We construct a malicious OS kernel

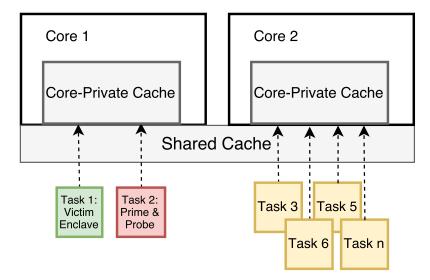

module that periodically applies the popular Prime and Probe attack [46] in the local cache of physical processor core, i.e., core-private cache, thereby recovering high-resolution information about the memory addresses that the target enclave accesses. By default, the OS tries to maximize the resource usage by spreading the tasks among all the cores which reduces the applicability of core-private channels. On the contrary, as the compromised OS schedules only the victim and attacker in the same core, the usage of core-private resources is prone to the system activity noise.

Tracking memory accesses of an enclave with high temporal (precision over the execution time) and spatial (precision over the memory space) resolution can be exploited in many application scenarios, i.e., any security data driven computation. We attack several AES implementations running inside the SGX enclave to demonstrate the power of our proposed side channel setup. In particular, we take advantage of our high resolution channel to construct more efficient key recovery attacks against several AES implementations, including those exploited in previous works [35] and those that are impossible to exploit without a high spatial resolution channel. Furthermore, we show that cache prefetching and S-box implementations as countermeasures are ineffective to prevent key recovery attacks, and they facilitate the memory trace extraction in some cases. In brief, this work:

- Presents a powerful high-bandwidth covert channel implemented through the core-private cache by exploiting several system resources in lieu of a compromised OS. The covert channel can be applied against TEEs to recover fine grained information about memory accesses, which often carry sensitive information.

- Demonstrates the high quality of our covert channel by recovering AES keys with less traces than in previous practical attacks, and further, by attacking implementations considered resistant to cache attacks.

- Shows that some of the countermeasures that were supposed to protect AES implementations, e.g. prefetching and S-box implementations, are ineffective in the context of SGX. In fact, prefetching can even be helpful to the attacker.

### 1.3 Outline of the work

In Chapter 2 we start by discussing the background information on Intel architecture and particularly SGX, Micro-architectural Side-Channel Attack and Prime and Probe. Then, we introduce the design of our side channel in Chapter 3 and discuss other methods to create low noise channels in adversarial operating system scenarios. After explanation of the implementation of our attack, in chapter 4, we talk about AES and its various common implementations. We show the results of our attack on these implementation in chapter 5, and conclude the work in chapter 6.

# Chapter 2

# Background & Related Work

Intel introduced some modifications to its processors released after the Skylake generation, and proposed a new programming model to make hardware based TEE available on commodity processors. However, SGX is a compatible extension based on the Intel architecture and its core has remained untouched. Significant modifications include integration of a memory encryption engine (MEE) hardware and support for a new set of processor instructions designed for enclave specific operations. On top of that, previous concepts that apply to cache memory and cache based timing side-channels are still applicable.

This chapter covers topics that help understand the side channel used in our key recovery attacks against SGX. We discuss the basic functionality of Intel SGX and possible micro-architectural attacks that can be deployed. After a brief discussion of Intel cache architecture, we finally explain the main procedure of the Prime and Probe technique which is used as part of our attack. Finally, we discuss the related work in the literature.

### 2.1 Intel SGX

SGX is a new subset of CPU instructions. It allows execution of software inside isolated environments called *enclaves*. Enclaves are user-level modules isolated from other software components running on the same hardware, including compromised OSs. SGX has recently gained popularity among the research community and various security applications have been proposed [4, 5, 12, 44, 50, 53, 24].

Enclave modules are developed as the trusted components of an application, and can be shipped and be loaded by untrusted components. The untrusted components interact with the system software, and the system software dedicates pages from a trusted memory region for the enclave by executing specific privileged instructions. The trusted memory region known as Enclave Page Cache (EPC) is configured through system BIOS and preallocated at boot time. After that, during the execution of the user application, the authenticity, integrity and confidentiality

Figure 2.1: Enclave Memory Access: After the traditional page table checks, the processor verifies if memory access to the trusted memory region should be permitted

of a running enclave are provided and measured by the processor.

Any untrusted execution, including the OS, has no control over the trusted memory region. Untrusted applications can only use specific instructions to call trusted components through predefined interfaces. Memory accesses to an address within the EPC range goes through additional vetting, and the processor blocks unwanted memory accesses trying to access EPC pages. Figure 2.1 shows the enclave specific memory access checks.

In summary, SGX assumes only the hardware to be trusted; any other agent is considered susceptible of being malicious. Although, the (potentially) compromised OS is in charge of the memory page mapping, SGX detects any malicious mapping performed by it. In fact, any alteration of the enclave pages from the OS is stored by SGX and is verifiable by the third party agents. This design helps developers to benefit from the hardware isolation for security critical applications. Figure 2.2 differentiate the attack surface of enclave trusted modules and other untrusted components.

Apart from the processor level access control that protects enclave pages from software adversaries snooping on them, SGX is also designed to protect enclaves from malicious physical adversaries monitoring system buses. When the operating system requests from the processor to dedicate EPC pages and map the enclave module, those pages in DRAM memory are encrypted and signed by the hardware. Pages are only decrypted when they are moved to the cache and their signatures are verified at the same time. MEE which resides between DRAM and LLC is responsible for these cryptographic operations.

# 2.1.1 Memory Encryption Engine (MEE)

MEE is designed as a subcomponent of Memory Controller (MC) [27]. An internal cache that accommodates a small but fast memory is the first place for processor

Figure 2.2: a) Left: attack surface without enclave. b) Right: Attack surface of enclave modules with Intel SGX technology

to resolve memory transactions. If the transaction can not be serviced by cache, it goes to MC. MC only utilizes cryptographic features provided by MEE to resolve memory accesses to the trusted region. The trusted region consists of EPC and its metadata which holds the mapped enclave pages and an integrity tree. In addition to the encryption/decryption of the cache lines on write/read operation from DRAM, MEE initiates additional transactions to update/verify the authentication tags with respect to the integrity tree. The root of trust for the MEE integrity tree is stored on an on-die SRAM which is not accessible outside of the processor package. Figure 2.3 illustrates MEE operations.

Note that, the aforementioned cryptographyic operations use two separate keys for authentication and encryption. These keys are generated randomly at boot from a random unique 256-bit entropy hardcoded into the processor, and they never leave the processor trusted boundary. Any modifications of the integrity tree to perform active attacks are detected at runtime and cause the processor to halt. The potential active (physical) adversary can not avoid the halt and reboot of the machine. Afterward, the processor has to generate new random keys.

# 2.2 Cache Memory

Modern computers use a hierarchical memory model with a different capacity and speed at each level. In this hierarchy, registers are the closest and fastest, but most expensive memories available to the processor. Most of the registers (depending on their role) are directly accessible from the software stack, i.e., OS, Compiler, etc. As processors have a limited number of registers, DRAMs are the next programmable memory in this hierarchy. The processor, with the help of the OS, maps memory pages from disk and other storage peripherals to DRAM. These peripherals and

Figure 2.3: MEE Operation: Transactions to the trusted region are issued with MEE involvement

disks are significantly slower compared to DRAM memory.

In this hierarchy, there is still a gap between the processor and DRAM memory speed. To avoid high latency, due to the data dependent instructions, modern processors take advantage of some levels of internal cache memory. In particular, Intel processors use three levels of cache known as the L1, L2 core-private caches and the L3 or Last Level Cache (LLC). LLC is shared among all physical cores in the processor. There are two L1 caches to separately store data and instructions known as L1D and L1I respectively. Figure 2.4 shows the memory hierarchy of a modern Intel based computer.

In general, when the processor tries to read data from a memory address, the request is issued to the closest cache level in the hierarchy. If that cache level misses the access, it passes to the next cache level, and finally fetches the data from DRAM. The next time, the processor does not read the data from DRAM memory. It fetches the data from the closest available cache, unless the data has changed or the cache block has been evicted.

The cache read/write operations are performed in cache lines. The line size is 64 bytes in most processors. Caches are smaller and faster as they are closer to the processor, and they are in general much smaller than DRAM memory. To be able to cache the DRAM data to different levels of cache hierarchy and utilize it in a simple but efficient way, an addressing schema and a coherency and replacement policy are needed to be enforced.

Cache, unlike others, is not directly addressable and programmable from the software stack. However, the software can use some instructions and side effects to manage the usage of cache memory. The knowledge of the enforced addressing schema and policies are important to engineer cache usage in a predictable manner. In the next subsections, these concepts are briefly explained.

Figure 2.4: Memory hierarchy of a modern computer

### 2.2.1 Cache Addressing Schema

Each level of cache is grouped into n sets, and each set can store m number of lines, i.e., m-way associative. The physical address is used to position the data in the cache. With a line size of b-byte, the lower  $\log_2 b$  bits of the physical address are used to index the byte in a line, and the next  $\log_2 n$  bits select the set that the line is mapped to.

In our target architecture, we have 32 kB of L1D and 32 kB of L1I cache to store data and instructions respectively. In L1D, there exists 64 sets and each set is 8-way associative. It should be noted that the line size is 64 byte. We used L1D as our side channel primitive. Figure 2.5 illustrates the cache addressing schema for L1D.

# 2.2.2 Cache Coherency and Replacement policy

In a multi-processor system with different levels of cache, maintaining data for the same address between different caches is a challenge. For example, if two physical cores try to process data from the same address, there is a chance that one core updates its core-private caches with the latest information, while the other core uses the outdated information.

To avoid such synchronization problems, there are different policies that can be adopted, e.g., not to cache shared data. For simplicity, the general approach used on our target processor is for the L3 cache to be inclusive of the L1 and L2 cache, which means the same data as L1 and L2 should be present for L3. On top of that, if a cache line is evicted from the L3 cache, it will be evicted from L1 and L2 but not reversely. As a result, in our attack on L1, filling a cache line will fill corresponding L2 and L3 lines, but evicting the same cache line will not affect L2 and L3. This behavior is important for the construction of cache eviction policy in our attacks.

The policy that is used to evict a line within a set is another important behavior.

Figure 2.5: L1D Cache Addressing Schema

As mentioned, several addresses can be mapped to the same set. When a set is full, the processor frees space for the upcoming cache lines. It needs to decide which line to evict beforehand. The most common cache replacement policy is Least Recently Used (LRU), which discards the least recently used item first. This behavior makes Prime and Probe attack (explained in the next section) more reliable, since an adversary who tries to fill all the cache lines of a set will not be worried to accidentally evict its own cache lines. Our target processor uses an adaptive LRU approach. In our experiments, we assume that it is a simple LRU cache replacement, since the adaptive behavior is unknown. Our experiments show that the amount of noise added due to its adaptive behavior is negligible.

### 2.3 Microarchitectural Attacks in SGX

Despite all the protection that SGX offers, the documentation specifically claims that side channel attacks were not considered under the threat scope in its design [18, 33]. In fact, although dealing with encrypted memory pages, the cache utilization is performed in a decrypted mode and concurrently to any other process in the system. This means that the hardware resources can be utilized as covert channels by both malicious enclaves and OSs. While enclave-to-enclave attacks have several similarities to cross-VM attacks [51], malicious OS-to-enclave attacks can give attackers a new capability not observed in other scenarios: virtually unlimited temporal resolution.

The OS can interrupt the execution of enclave processes every small number of accesses to check the hardware utilization, as just the TLB cache (but no other cache) is flushed during context switches. Further, while cross-core attacks gained huge popularity in others scenarios (e.g. clouds or smartphones) for not requiring core co-residency, a compromised OS can assign an enclave execution any core of its choice, and therefore use any core-private channel. Thus, while SGX can prevent untrusted software to perform Direct Memory Access (DMA) attacks, it also

gives almost full resolution for the exploitation of hardware covert channels. For instance, an attacker can exploit page faults to learn about the memory page usage of the enclave process [56, 62]. Further she can create contention and snoop on the utilization of any core-private and core-shared hardware resource, including but not limited to Branch Prediction Units (BPUs), L1 caches or LLC caches [1, 46, 40].

The applicability of DRAM based attacks like the rowhammer attack seems infeasible due to the protection and isolation that the enclaves perform on DRAM memory pages. Further, although applicable in other scenarios [9], execution of enclave do not update the Branch Trace Store (BTS) and Processor Trace (PT), and these can not provide (at least directly) information about the isolated process.

From the aforementioned resources, the resource that gives most information is the hardware cache. Unlike page faults, which at most will give a granularity of 4kB, cache hits/misses can give 64 byte utilization granularity (depending on the cache line size). In addition, while other hardware resources like Branch Prediction Units (BPU) can only extract branch dependent execution flow information, cache attacks can extract information from any kind of memory access. Although most prior work targets the LLC for being shared across cores, this is not necessary in SGX scenarios, local caches are as applicable as LLC attacks.

In summary, because caches are not flushed when the enclave execution is interrupted, the OS can gain almost unlimited timing resolution. Table 2.1 compare the discussed channels. In short, the processor core-private cache, and in particular L1 cache is the channel that gives us the highest resolution, lowest noise and can target both code and data.

Table 2.1: Comparison of different side-channels and their applicability to attack enclave.

| Channel    | $\mathrm{CPC^1}$ | $LLC^2$   | $\mathrm{BP}^3$ | $\mathrm{PF}^4$ | $\mathrm{TLB}^5$ | $ m RH^6$ |

|------------|------------------|-----------|-----------------|-----------------|------------------|-----------|

| Possible   | Yes              | Yes       | Yes             | Yes             | No               | No        |

| Resolution | 64 byte          | 64 byte   | Branches        | $4\mathrm{kB}$  | N/A              | N/A       |

| Noise      | Local            | Global    | Local           | N/A             | N/A              | N/A       |

| Target     | Data+Code        | Data+Code | Code            | Data+Code       | N/A              | N/A       |

<sup>&</sup>lt;sup>1</sup> Core-Private Cache; <sup>2</sup> Last-Level Cache; <sup>3</sup> Branch Predictor Cache;

#### 2.3.1 Prime+Probe

The Prime+Probe attack was first introduced in [46] as a spy process capable of attacking core-private caches. It was later expanded to recover RSA keys [2], keystrokes in commercial clouds [49] and El Gamal keys across VMs [66]. Later the attack was shown to be applicable also in the LLC [40, 34]. As our attack is carried

<sup>&</sup>lt;sup>4</sup> Page Fault; <sup>5</sup> TLB Cache; <sup>6</sup> Rowhammering

out in the L1 caches, we do not describe the major hurdles (e.g. slices) that an attacker would have to overcome to implement it in the LLC. The Prime+Probe attack is mainly implemented in 3 stages:

- **Prime Stage:** in which the attacker fills the entire cache or a small portion of it with her own junk data.

- Victim Access Stage: in which the attacker waits for the victim to make accesses to particular sets in the cache, hoping to see data dependent cache set utilization. Note that, in any case, victim accesses to primed sets will evict at least one of the attackers junk memory blocks from the set.

- **Probe Stage:** in which the attacker performs a per-set timed re-access of the previously primed data. If the attacker observes a high probe time, she deduces that the cache set was utilized by the victim, as at least one of the memory blocks came from the memory. On the contrary, if the attacker observes low access times, she deduces that all the previously primed memory blocks still reside in the cache set, i.e., it was not utilized by the victim.

Thus, the Prime and Probe methodology allows an attacker to guess the cache sets utilized by the victim. In the L1 cache in particular, this information can be used to determine the lower bits of the accessed physical address. Further, the translation of virtual to physical address does not affect the lower 16 bits of the address. This lets an attacker to infer which offset within a memory page of the victim has been accessed. This information can be exploited in many privacy and security critical applications. For example, A full key recovery attack can be mounted if the algorithm has key-dependent memory accesses that are translated into different cache memory accesses.

# 2.4 Side-Channel Attacks & SGX

Side-channel attacks have been studied for many years. On a local area network having relatively accurate timing measurement, the timing of the decryption operation on a web server could reveal enough information about private keys stored on the server [15]. Timing attacks are capable of breaking important cryptography primitives, such as Diffie-Hellman exponent and factor of RSA keys [36]. More specifically, microarchitectural timing side channels have been explored extensively [25]. The first few attacks proposed were based on the timing difference between L1/L2 core private cache misses and hits.

#### Microarchitectural Side-Channels

Generally, microarchitectural timing attacks are based on the fact that a spy process is capable of using a resource shared with the victim, and utilize that to measure timing differences of various victim operations. The difference of access time to the shared cache is sufficient for an attackers to create a side channel to a victim process and infer memory access patterns of that process. In the earlier days, these attacks reflected the effectiveness of this technique to recover cryptography keys of ciphers such as DES [60], AES [10] and RSA [47]. Although there exist solutions to make cryptographic implementation resistant to cache attacks [13, 46], the adoption of these solutions are limited due to worse performance. Further, cache attacks are capable of extracting information from non-cryptographic applications [65].

More recent proposals applied cache side channels on shared Last Level Caches (LLC), a shared resource among all the cores. This is important as, compared to previous core-private attacks, LLC attacks are applicable even when attacker and victim reside in different cores. The Flush+Reload [63, 6] LLC attack is only applicable to systems with shared memory. Flush+Reload can be applied across VMs [35], in Platform As a Service (PaaS) clouds [65] and on smartphones [39]. The Flush+Reload attack is less prone to noise, as it depends on the access to a single memory block. However, it is constrained by the memory deduplication requirement.

Prime and Probe [40], shows that in contrast to the previous L1/L2 core private cache side channels and the Flush+Reload attack, practical attacks can be performed without memory deduplication or a core co-residency requirement. The Prime and Probe attack, unlike Flush+Reload, can be implemented from virtually any cloud virtual machines running on the same hardware. The attacker can identify where a particular VM is located on the cloud infrastructure such as Amazon EC2, create VMs until a co-located one is found [49, 64] and perform cross-VM Prime and Probe attacks [34]. Prime and Probe can also be mounted from a browser using JavaScript [45] and as a malicious application on smartphones [39]. These side channels can be improved by causing a denial of service to the Linux CFS scheduler [28].

In addition to caches, Branch Target Buffer (BTB) is a shared processor cache used to predict the target of a branch before its execution. It can be exploited to determine if a branch has been taken by a target process or not [1, 38]. More recently, BTB has been exploited to bypass Address Space Layout Randomization (ASLR) [23].

#### Intel SGX Attack & Defence

Intel SGX has been analyzed based on the available resources from Intel [18]. A side channel resistant TCB is proposed in the literature [19]. However, the proposed solution requires significant changes to the design of the processor and it adds performance penalties that may not be desirable. Similar to Intel SGX, ARM TrustZone is vulnerable to side-channel attacks [39]. Control-Channel attack [62] has further been proposed using page-fault as a side channel. An adversarial OS can introduce page faults to a target application and, based on the timing of the accessed page, the

execution flow of a target can be inferred at page size granularity. Another possible attack on SGX can exploit race conditions between two running threads inside an enclave [61].

Runtime control flows inside SGX can be inferred using BTB [38]. However, data dependent table based computations, e.g., AES T-Table and S-Box implementations are not vulnerable to this side channel. It has been demonstrated that LLC side-channels can be mounted from one enclave to another one [51]. This is similar to previous LLC attacks proposed outside of the SGX context with a specific method to find physical address of the enclave page. Similar to our work, using core-private cache as a side channel has recently been released on eprint servers independent of our work [11]. In contrast, their attack is not based on the interruption of the target, is focused on stealthiness, and has a much lower resolution.

On the more defensive proposals, page fault side channels that are effective on SGX can be defeated using software solutions [56] or by using an additional extension of Intel processors named TSX [55]. In the latter, a user level application can detect the occurrence of a page fault before passing it to the OS and terminate itself in the face of malicious page fault patterns. In other proposals, SGX-Shield [52] adds ASLR protection and introduces software diversity inside an enclave. Lastly a tool named Moat [57] allows developers to verify security of an enclave application based on different adversarial models.

# Chapter 3

# Cache Side-Channel Attack on SGX

# 3.1 Attack Design

We explain how to establish a high resolution channel from a compromised OS to monitor an SGX enclave. Such an attack allows fine-grained information leakage. To achieve this goal with our system level adversarial model, we exploit features of the operating system to create an accurate low noise channel.

We construct our attack by: (1) partitioning the available cache between the victim task running an enclave module and the rest of the system running core operating system kernel threads and every other running tasks. Afterwards, we do not want to measure cache hit/miss of the whole enclave at once since the execution of the enclave module may cause lots of memory accesses in one run. And the bigger the computation of the enclave module, the more noise. That is one of the limitations of previous cache side-channel attacks that the adversary has to run the target service or task many times and perform the attack using statistical data which the leaked information is more limited.

To avoid that, (2) we measure the target enclave one step at a time and in each step, the processor executes the target for a short amount of time. After we measured all the steps (or only the necessary steps), we can map the collected traces to the target enclave binary to extract security critical information. In this section, we first describe attacker capabilities, and then our main design goals.

#### 3.1.1 Adversarial Model

In our attack, we assume that the adversary has root level access to a system running Intel SGX SDK. Attacker is capable of installing kernel modules and configuring boot properties of the machine. In addition, the attacker is capable of scheduling the execution of an enclave and the measurement tool at the same time. These assumptions are reasonable, as SGX promises a trusted environment for code ex-

ecution on untrusted systems. For example, The adversary could be a malicious cloud provider hosting a malicious OS, the root level access could have been gained through exploiting kernel services or social engineering, or the adversary has gained physical access to the system and can modify the the OS image on the disk. All of these are practical examples that SGX is proposed to protect against.

The attacker also should have access to the target enclave binary, and for simplicity, we assume the binary is not obfuscated. Access to the binary is inherent to the root access on the OS. However, obfuscation could increase the defense bar and makes it harder to infer security critical information from the collected memory access patterns. This complexity is outside of the scope of this work, and is irrelevant to our goal of exploring the main security problem.

### 3.1.2 Cache Partitioning & Noise Reduction

By default, the OS tries to maximize the performance of the available hardware resources by sharing them among different tasks. Parallel execution of different tasks scheduled on the same hardware adds significant noise to the main attack channel. In the design of our malicious OS, we want to use part of the available cache as an isolated channel resistant to the outside noise. Although having an ideal channel is optimistic, we can exploit OS functionalities to reduce the noise as much as possible. We can create a noise resistant, high bandwidth channel using the following design choices:

- Scheduling only the target and the spy Prime and Probe code on one of the physical cores, and dedication of other physical cores to all other running operations. This isolates the core-private cache of a physical core from the rest of the system, thus leaves the spy and the target an isolated core-private channel.

- Core isolation will not work if we want to use the shared cache among the processor cores such as LLC. However, we can force the virtual to physical page mapping to always map specific pages to physical addresses that target specific sets in the shared cache. Having that, we can map the target and spy pages to a subset of shared cache sets, and map every other memory page on the system to the remaining sets.

- It is possible to disable caching behavior for specific physical addresses. This significantly reduces the performance of the running tasks that uses those memory addresses. This method can not be used as a global system-wide option to disable the noise for all OS relevant memory accesses. Yet, this can be used on a case by case basis to reduce noise of a specific physical page.

- Configuration of CPU features available on the modern processors that affect frequency to maintain a stable clock frequency. These configurations help to

Figure 3.1: Scheduling the noisy tasks on a separate core from the victim & spy to create a core-private isolated channel.

have a pseudo-constant execution speed for all the instructions. This is useful to avoid variable time measurement during the probe step. Having a constant execution speed reduces the noise of eviction time thresholds.

In our attack, we use the isolated core-private cache as our channel, and configure the processor to have a constant frequency. Figure 3.1 illustrates the design of this channel.

### 3.1.3 Step by Step Execution

The longer the victim enclave runs without interruption, the higher the number of accesses made to the cache, implying higher noise and less temporal resolution. We force the enclave execution to be interrupted after short time intervals, in order to identify all enclave memory accesses. We name a small number of instructions inside and enclave executed without interruption, an execution unit. Here are the steps that we take in our attack tool:

- 1. Initialize the required memory pointers used during Prime and Probe.

- 2. Start the interrupt service to interrupt an isolated core after every small number of cycles.

- 3. Schedule the victim enclave on the same core.

- 4. The victim enclave will be interrupted.

- 5. Probe access times for all of the cache sets (which is potentially affected by the previous execution unit).

- 6. Store the measured access times to a separate buffer.

- 7. Prime all the target cache sets for probing the next execution unit.

- 8. Continue the execution until the next interrupt at step 4.

The loop in the aforementioned steps happen as far as we are interested in the measurement. Afterward, we stop the interrupt service to restore the core behavior to its normal state. Parallel to the above operations, we can schedule a task on another core without adding noise to our isolated channel to transfer the measurement buffer to the disk for real time or offline analysis of measured memory accesses.

### 3.1.4 Summary

By having the mentioned two elements, even a comparably small cache memory like the L1 cache turns into a high capacity channel with 64 byte granularity, as every major processor features 64 byte cache lines. Note that our spy process monitors the L1D cache, but can also be implemented to monitor in the L1I or last level caches. Our spy process is designed to profile all the sets in the L1D cache with the goal of retrieving the maximum information possible.

We should further reduce other possible sources of noise, e.g., context switches. The main purpose is that the attacker can cleanly retrieve most of the secret dependent memory accesses made by the target enclave. Note that the attacker can directly identify the set number that static data and instructions from the victim binary will occupy, as she has access to it. Since the L1 cache is virtually addressed, knowing the offset with respect to a page boundary is enough to know the accessed set.

# 3.2 Attack Implementation

We explain the technical details behind the implementation of our attack tool, in particular, how the noise sources are limited and how we increase the time resolution to obtain cleaner traces. We separate the implementation of our attack to the following three main components:

- Eviction Set: The construction of the logic and code that we used to accurately perform Prime and Probe on L1D set.

- Noise Reducing Configuration: The configuration and modification that we make dynamically to the OS.

- Malicious Kernel Driver: The malicious kernel driver that program the OS interrupt handler and perform the attack steps.

We explain the detail of each of the components in the following subsections.

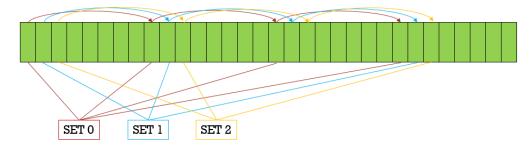

Figure 3.2: Pointers with addresses associated to the same set are initialized. It helps to reduce the number of instructions required to fill each set.

#### 3.2.1 Eviction Set

The access times to L1 and L2 caches only differ in around 5 cycles and we want to Prime and Probe the entire L1D cache at each sampling, any unwanted memory access adds some amount of noise and reduces our channel capacity. To cope with this issue we use pointer chasing to Prime and Probe the 8-way sets, and C macro programming to repeat our Prime and Probe code stubs; which removes any unwanted memory access to the local stack pointer that might add noise and reduce the footprint of the obtained trace.

In pointer chasing approach, we initialize a memory buffer with linked lists of pointers associated to the same set. Having a buffer initialized like Figure 3.2, we can easily read all the addresses with only one instruction per read. Reducing the number of instructions that we execute on each sampling decreases the measurement time. Further, the dependency of access to each pointer on the previous one helps to avoid out-of-order execution of the instructions. Listing 3.1, 3.2, show the assembly code stubs that we used for our prime and probe stub. Note that, out-of-order execution of Prime and Probe operations adds an unpredictable noise, which is not acceptable.

```

mfence;

mov (%rbx), %rbx;

```

Listing 3.1: Prime assembly code (AT&T syntax): Traversing the pointers.

```

mov %rax, %r10;

mfence:

rdtsc;

mov %eax, %ecx;

mov (\%rbx), \%rbx;

lfence:

rdtsc;

sub %rax, %rcx;

mov \%r10, \%rax;

neg %rcx;

```

Listing 3.2: Probe assembly code (AT&T syntax): Traversing the pointers and measuring the time using rdtsc instruction.

### 3.2.2 Noise Reducing Configuration

The target Linux OS schedules different tasks among available logical processors by default. The core of the Linux scheduler which has been implemented in ... /kernel/sched/core.c and the main scheduler function \_\_schedule is triggered on every tick of the logical processor's local timer interrupt. One way to remove a specific logical processor of the default scheduling algorithm is through the kernel boot configuration isolcpus which accepts a list of logical cores to be excluded from scheduling. To avoid a logical core from triggering the scheduling algorithm on its local timer interrupt, we can use nohz\_full boot configuration option, which similarly receives a list of logical processors as parameter.

Recall that reconfiguring the boot parameters and restarting the OS is included in our attackers capabilities. However, these capabilities are not necessary, as we can walk through the kernel task tree structure and turn the PF\_NO\_SETAFFINITY flag off for all tasks. Then, by dynamically calling the kernel sched\_setaffinity interface for every task, we are able to force all the running kernel and user tasks to execute on specific processors. In addition to tasks and kernel threads, interrupts also need to be isolated from the target core. Most of the interrupts can be restricted to specific cores by configuring smp\_affinity, except for the non-maskable interrupts (NMIs), which cannot be avoided. However, in our experience, the occurrence of

```

# Boot Configurations:

# isolcpus=1,3

# nohz_full=1,3

# Disable logical CPU pairs

echo 0 > /sys/devices/system/cpu/cpu2/online

echo 0 > /sys/devices/system/cpu/cpu3/online

# Set IRQ affinity mask to CPU 0

cd /proc/irq/

echo 1 | tee */smp_affinity

# Set CPU frequency scaling to performance mode

cd /sys/devices/system/cpu/

echo performance | tee cpu*/cpufreq/scaling_governor

echo 3050000 | tee cpu*/cpufreq/scaling_max_freq

echo 3010000 | tee cpu*/cpufreq/scaling_min_freq

```

Listing 3.3: Malicious OS Configuration

them is negligible and does not add noise to our channel.

CPU frequency has a more dynamic behavior in modern processors. Our target processor has **Speedstep** technology which allows dynamic adjustment of processor voltage and **C-state**, which allows different power management states [20]. These features, in addition to hyper-threading (concurrent execution of two threads in the same physical core), make the actual measurement of cycles through *rdtsc* less reliable. *rdtsc* instruction returns the number of cycle since reboot. Cache-side channel attacks that use this cycle counter are affected by the dynamic CPU frequency, as it affects the number of cycles it takes to execute an instruction. In non-system adversarial scenarios, these noise sources have been neglected thus forcing the attacker to do more measurements. In our scenario, these processor features can be disabled through the computer BIOS setup or can be configured by the OS to avoid unpredictable frequency. In our attack, we simply disabled every second logical processor to practically disable the hyper-threading feature.

To have a stable frequency in spite of the available battery saving and frequency features, we set the CPU scaling governor to **performance** and limited the maximum and minimum frequency range. In our experiment, these configurations that can be done from a root shell effectively reduces the noise of our isolated channel. Listing 3.3 shows the configurations during our experiments.

#### 3.2.3 Malicious Kernel Driver

Aiming at reducing the number of memory accesses made by the victim between two malicious OS interrupts, we use the local APIC programmable interrupt, available on each processor core. The APIC timer has different programmable modes but we are only interested in the **TSC-Deadline** mode. In TSC deadline mode, the specified TSC value will cause the local APIC to generate a timer IRQ once the CPU reaches it. In the Linux kernel, the function lapic\_next\_deadline is responsible for setting the next deadline on each interrupt. The actual interrupt handler code for this IRQ is the function local\_apic\_timer\_interrupt. We exploit the first function to set the TSC deadline to an arbitrary value and the second function to execute our Prime and Probe attack code.

In order to enable and disable our measurment tool as needed at runtime, we install hooks on these two functions. A look at the disassembly of these functions reveals that there are calls to a null function at the beginning that can be replaced by calls to the malicious functions of our kernel module.

In the modified lapic\_next\_deadline function, we set the timer interrupt to specific values such that the running target enclave is interrupted every short period of execution time, thus the target processor trigger the interrupt in short periods and leave the actual running target enclave a short period of execution time.

In the modified local\_apic\_timer\_interrupt, we first probe the entire 64 sets of the L1D cache to gather information of the previous execution unit and then prime the entire 64 sets for the next execution. After each probe, we store the the retrieved cache information from the sampling of the L1 D cache to a separate buffer in kernel memory. Our kernel driver is capable of performing 50000 circular samplings.

To be able to run our attack code against the execution inside the enclave, we need to start and end our attack at the time the target process is inside the enclave. For this purpose, our kernel driver supports two *ioctl* interfaces to install/uninstall the attack timer hooks. In the user level, we enable the attack timer interrupt before the call to the enclave interface and disable it right after.

# Chapter 4

# **AES** in Practice

Advanced Encryption Standard (AES) is a subset of an original cipher named Rijndael after Vincent Rijmen and Joan Daemen [21]. It is a standard by National Institute of Standards and Technology (NIST). The following gives a detailed description of AES and its various implementations to help the reader understand the attacks that we later perform. AES is a widely used symmetric block cipher that supports three key sizes from 128 bit to 256 bits. Our description and attacks focus on the 128-bit key version, AES-128, but most attacks described can be applied to larger-key versions as well. AES is based on 4 main operations: AddRoundKey, SubBytes, ShiftRows and MixColumns and a state table initialized to the plain text. Algorithm 1 shows the main procedure of AES encryption function.

#### Algorithm 1 AES Encryption

```

1: procedure ENCRYPT

2:

i \leftarrow 0

ExpandKeys

3:

AddRoundKey(i)

4:

5: round:

SubBytes

6:

ShiftRows

7:

MixColumns

8:

9:

AddRoundKey(i)

10:

i \leftarrow i + 1

if i < n - 1 then

11:

goto round

12:

13:

SubBytes

14:

ShiftRows

AddRoundKey(i)

15:

```

The input block size for AES is 128 bits but the operations are performed on a byte granularity. AES consists of a state table and n rounds of repeated operations

which n depends on the key size. In case of 128-bit key version, n is equal to 10. At the initial step of the procedure, the cipher key is expanded to the round keys used in each round individually and the state table is initialized with the input block. The last round ends with a final key addition without any MixColumns operation. The main leakage source in AES implementations comes from the fact that they utilize state-dependent table look up operations for the SubBytes operation. SubBytes replace each byte of the state table with the corresponding output of a non-linear function.

Rather than calculating the output of the function each time at runtime, a precomputed 256 entry substitution table known as S-Box is used. These look-ups result in secret-dependent memory accesses that can be exploited by cache attacks and leak information about the round keys. In practice, a total of a 160 accesses are performed to the S-box during a 128-bit AES encryption, 16 accesses per round. We refer to this implementation as the S-box implementation.

# 4.1 T-Table Implementations

For performance improvements, some implementations combine the MixColumns and SubBytes in a single table lookup. At the cost of bigger pre-computed tables (and therefore, more memory usage) the encryption time can be significantly reduced. The most common type uses 4 T-tables: 256 entry substitution tables, each entry being 32 bits long. Listing 4.1 shows the summarized T-Table implementation of AES. The entries of the four T-tables are the same bytes but rotated by 1, 2 and 3 positions, depending on the position of the input byte in the AES state table ①. Each rounds of operation is summarized to four statements consist of a series of 32-bit operations ②. We refer to this as the 4 T-table implementation.

Aiming at improving the memory usage of T-table based implementations, some designs utilize a single 256 entries T-table, where each entry is 64 bits long. Each entry contains two copies of the 32 bit values typically observed with regular size T-tables. This design reads each entry with a different byte offset, such that the values from the 4 T-tables can be read from a single bigger T-table. The performance of the implementation is comparable, but requires efficient non word-aligned memory accesses. We refer to this as the Biq T-table implementation.

T-Table based implementations of AES have extensive memory footprints. The memory accesses to the 4 T-tables and Big T-Table will be issued over 64 and 32 sets respectively. As distinguishing memory accesses over more sets are easier to observe, these implementation are highly vulnerable to cache side channels.

```

0 1

static const u32 Te0[256] = \{0xc66363a5U, \ldots\};

static const u32 Te1[256] = \{0xa5c66363U, \dots\};

static const u32 Te2[256] = \{0x63a5c663U, \dots\};

static const u32 Te3[256] = \{0x6363a5c6U, \dots\};

5

6

for (;;) {

2 7

t0 = Te0[(s0 >> 24)]

Te1[(s1>>16)\&0xff] Te2[(s2>>8)\&0xff]

^{\circ} Te3 [ (s3)&0xff ]

rk [4];

8

9

t1 = Te0[(s1>>24)]

Te1[(s2>>16)\&0xff] Te2[(s3>>8)\&0xff]

^{\text{Te3}}[(s0)\&0xff]

rk [5];

10

t2 = Te0[(s2>>24)]

Te1[(s3>>16)\&0xff] 	 Te2[(s0>>8)\&0xff]

11

12

^{\circ} Te3 [ (s1)&0xff ]

rk [6];

t3 = Te0[(s3>>24)]

Te1[(s0>>16)\&0xff] 	 Te2[(s1>>8)\&0xff]

13

^{\circ} Te3 [ (s2)&0xff ]

14

rk [7];

15

```

Listing 4.1: AES 4 T-Table Encryption, Each T-Table consists of a shifted variation of the same 32 bit values. The round keys stored as 32 bit values (rk) will be added on each round.

# 4.2 Non-vulnerable Implementations

There are further efficient implementations of AES that are not susceptible to cache attacks, as they avoid secret-dependent memory accesses. These implementation styles include bit-sliced implementations [41], implementations using vector instructions [29], constant memory access implementations and implementations using AES instruction set extensions on modern Intel CPUs [32].

However, the aforementioned implementations all come with their separate draw-backs. The bit-sliced implementations need data to be reformatted before and after encryption and usually show good performance only if data is processed in large chunks [8]. Constant memory access implementations also suffer from performance as the number of memory accesses during an encryption significantly increases. While hardware support like AES-NI combines absence of leakage with highest performance, it is only an option if implemented and if the hardware can be trusted [59], and further might be disabled in BIOS configuration options.

# 4.3 Table Prefetching as a Countermeasure

In response to cache attacks in general and AES attacks in particular, several cryptographic library designers implement cache prefetching approaches, which just load the key dependent data or instructions to the cache prior to their possible utilization. In the case of AES this simply means loading all the substitution tables to the cache, either once during the encryption (at the beginning) or before each round

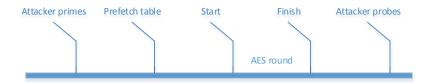

Figure 4.1: Prefetching and the timeline effect for a regular Prime and Probe attack

execution.

Prefetching takes advantage of the low temporal resolution that an attacker obtains when performing a regular non-OS controlled cache attack, as it assumes that an attacker cannot conduct an attack faster than the prefetching action. Translated to AES, prefetching assumes that a cache attack does not have enough temporal granularity to determine which positions in the substitution table have been used if they are prefetched, e.g., at the beginning of each round.

An example of the implications that such a countermeasure will have on a typical cache attack can be observed in Figure 4.1. The Prime and Probe process cannot be executed within the execution of a single AES round. Thanks to prefetching, the attacker is only able to see cache hits on all the Table entries.

We analyze whether those countermeasures, implemented in many cryptographic libraries, resist the scenario in which an attacker fully controls the OS and can interrupt the AES process after every small number of accesses. As it was explained in the background, attacking SGX gives a malicious OS almost full temporal resolution, which can reverse the effect of prefetching mechanisms.

# 4.4 Susceptibility to Cache Attacks

Depending on the implementation style, implementations can be more susceptible to cache attacks or less. The resolution an attacker gets depends on the cache line size, which is 64 bytes on all relevant modern CPUs, including Intel and most ARM cores.

For the **S-box** implementation, the S-box occupies a total of 4 cache lines (256 bytes). That is, an attacker able to observe each access to a table entry can learn at most two bits per access. Attacks relying on probabilistic observations of the S-box entries not being accessed during an entire encryption [35] would observe such a case with a probability of  $1.02 \cdot 10^{-20}$ , making a micro-architectural attack nearly infeasible. For a **4 T-tables** implementation, each of the T-tables gets 40 accesses per encryption, 4 per round, and occupies 16 cache lines. Therefore, the probability of a table entry not being accessed in an entire encryption is 8%, a fact that was

exploited in [35] to recover the full key.

In particular, all these works target either the first or the last round to avoid the MixColumns operation. In the first round, the intermediate state before the MixColumns operation is given by  $s_i^0 = T_i[p_i \oplus k_i^0]$ , where  $p_i$  and  $k_i^0$  are the plaintext and first round key bytes i,  $T_i$  is the table utilization corresponding to byte i and  $s_i^0$  is the intermediate state before the MixColumns operation in the first round. We see that, if the attacker knows the table entry being utilized  $x_i$  and the plaintext he can derive equations in the form  $x_i = p_i \oplus k_i^0$  to recover the key. A similar approach can be utilized to mount an attack in the last round where the output is in the form  $c_i = T_i[s_i^9] \oplus k_i^{10}$ . The maximum an attacker can learn, however, is 4 bit per lookup, if each lookup can be observed separately. The scenario for attacks looking at accesses to a single cache line for an entire encryption learn a lot less, hence need significantly more measurements.

For a Big T-table implementation, the T-table occupies 32 cache lines, and the probability of not accessing an entry is reduced to 0.6%. This, although not exploited in a realistic attack, could lead to key recovery with sufficiently many measurements. An adversary observing each memory access separately, however, can learn 5 bits per access, as each cache line contains only 8 of the larger entries.

Note that an attacker that gets to observe every single access of the aforementioned AES implementations would succeed to recover the key with significantly fewer traces, as she gets to know the entry accessed at every point in the execution. This scenario was analyzed in [16] with simulated cache traces. Their work focuses on recovering the key based on observations made in the first and second AES rounds establishing relations between the first and second round keys. As a result, they succeed on recovering an AES key from a 4 T-table implementation with as few as six observed encryptions in a noise free environment. These attacker capabilities could even turn micro-architectural attacks against S-box implementations practical.

# Chapter 5

# **AES Key Recovery Attack**

In this chapter, we discuss our key recovery attack analysis and results. First, we show the results on quality of our side channel. Afterward, we discuss three different cryptographic key recovery attacks on different implementations of AES using our attack tool. We also explain the effect of table prefetching in this context. In short we demonstrate the following attacks:

- Known plaintext attack (KPA) on T-Table using the leakage from first two rounds of AES operation.

- Known ciphertext attack (KCA) on T-Table using the leakage from last two rounds of AES operation.

- Known ciphertext attack (KCA) on S-Box using the leakage from last round of AES operation.

In all of the above attacks, we assume no knowledge of the key used inside the enclave, but we assume to have access to the enclave binary, and thus to the offset of the substitution tables in the enclave module. We obtained these implementations from latest OpenSSL & wolfSSL libraries, and compiled them with available flags to make different characteristics enabled/disabled.

### 5.1 Channel Measurement

We analyzed the capacity of our side channel. This section discusses our results on our channel quality, and explains how we used our observations to infer memory accesses.

# 5.1.1 Experimental Setup

Our experimental setup is a Dell Inspiron 5559 laptop with Intel(R) Skylake Core(TM) i7-6500U processor running Ubuntu 14.04.5 LTS and SGX SDK 1.7. Our target processor has 2 hyper-threaded physical cores. Each physical core has 32 kB of L1D

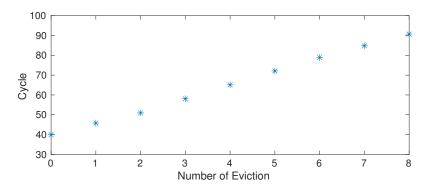

Figure 5.1: Average cycle count based on the number of evictions in a set.

Figure 5.2: Average cycle count for each sets. Variations are due to channel noise, making 5 sets unusable for our attack.

and 32 kB of L1I local cache memory. The L1 cache, used as our side channel, is 8-way associative and consist of 64 sets.

# 5.1.2 Eviction Set Quality

Even though Skylake processors do not always use the LRU cache replacement policy and have a more adaptive undocumented cache replacement policy [26], our results show that we can still use the pointer chasing eviction set technique to detect memory accesses. In the specific case of our L1D cache, the access time for chasing 8 pointers associated to a specific set is 40 cycles on average.

In order to test the resolution of our covert channel, we took an average of 50000 samples of all the sets and varied the number of evictions from 0 to 8. The results can be seen in Figure 5.1, where the access time is increased by roughly 5 cycles for every additional eviction. Thus, the results show that our eviction technique gives us an accurate measurement on the number of evicted lines within a cache set.

Figure 5.3: Cache hit map before filtering for context switch noise.

Figure 5.4: Cache hit map after filtering for context switch noise. Enclave memory access patterns are clearly visible once standard noise from context switch has been eliminated.

#### 5.1.3 Channel Bandwidth

Our isolated CPU core and the L1D eviction set have the minimal possible noise due to the removal of various source of noises such as variable CPU frequency, and the OS noise; however, the actual noise from the context switch between enclave process and attacker interrupt is mostly unavoidable.

The amount of noise that these unwanted memory accesses add to the observation can be measured by running an enclave with an empty loop under our attack measurement. Our results, presented in Figure 5.2, show that every set has a consistent number of evictions. Among the 64 sets, there are only 5 sets that get filled as a side effect of the context switch memory accesses. For the other sets, we observed either 0 or less than 8 unwanted accesses. Due to the consistency of the number of evictions per set, we can conclude that only sets that get completely filled are blind and do not reveal any information about the target enclave, 4 out of 64 sets in our particular case.

An example of the applied noise ex-filtration process can be observed in Fig-

ure 5.4, in which the enclave process was consecutively accessing different sets. It shows the access pattern retrieved from the enclave once the context switch noise access has been taking into account and removed. Figure 5.3 shows the hit access map, without taking into account the appropriate thresholds.

#### 5.2 AES T-Table KPA Attack

Our first attack target the T-table implementations. To recover the AES key from as few traces as possible in a known plaintext scenario, we observe the memory access pattern of the first 2 rounds of the AES function. A perfect single trace of the first round cache access information reveals at most the least significant 4 and 5 bits of each key byte in 4 T-table (16 entries/cache line) and big T-table implementations (8 entries/cache line) respectively.

As we want to retrieve the key with a minimal number of traces, we also retrieve the information from the accesses in the second round and use the relations between the first and second round key. In particular, we benefit from relations described in [16], who utilized simulated data to demonstrate the effectiveness of their AES key recovery algorithm. As our attack is close to getting all specific T-table accesses, their equations serve us the most efficient mechanisms to retrieve the key from the first two rounds information.

```

x_0^1 = 2s(p_0 \oplus k_0) \oplus 3s(p_5 \oplus k_5) \oplus s(p_{10} \oplus k_{10}) \oplus s(p_{15} \oplus k_{15}) \oplus s(k_{13}) \oplus k_0 \oplus 1

x_1^1 = s(p_0 \oplus k_0) \oplus 2s(p_5 \oplus k_5) \oplus 3s(p_{10} \oplus k_{10}) \oplus s(p_{15} \oplus k_{15}) \oplus s(k_{14}) \oplus k_1

x_2^1 = s(p_0 \oplus k_0) \oplus s(p_5 \oplus k_5) \oplus 2s(p_{10} \oplus k_{10}) \oplus 3s(p_{15} \oplus k_{15}) \oplus s(k_{15}) \oplus k_2

x_3^1 = 3s(p_0 \oplus k_0) \oplus s(p_5 \oplus k_5) \oplus s(p_{10} \oplus k_{10}) \oplus 2s(p_{15} \oplus k_{15}) \oplus s(k_{12}) \oplus k_3

x_4^1 = 2s(p_4 \oplus k_4) \oplus 3s(p_9 \oplus k_9) \oplus s(p_{14} \oplus k_{14}) \oplus s(p_3 \oplus k_3) \oplus s(k_{13}) \oplus k_0 \oplus k_4 \oplus 1

x_5^1 = s(p_4 \oplus k_4) \oplus 2s(p_9 \oplus k_9) \oplus 3s(p_{14} \oplus k_{14}) \oplus s(p_3 \oplus k_3) \oplus s(k_{14}) \oplus k_1 \oplus k_5

x_6^1 = s(p_4 \oplus k_4) \oplus s(p_9 \oplus k_9) \oplus 2s(p_{14} \oplus k_{14}) \oplus 3s(p_3 \oplus k_3) \oplus s(k_{15}) \oplus k_2 \oplus k_6

x_7^1 = 3s(p_4 \oplus k_4) \oplus s(p_9 \oplus k_9) \oplus s(p_{14} \oplus k_{14}) \oplus 2s(p_3 \oplus k_3) \oplus s(k_{12}) \oplus k_3 \oplus k_7

x_8^1 = 2s(p_8 \oplus k_8) \oplus 3s(p_{13} \oplus k_{13}) \oplus s(p_2 \oplus k_2) \oplus s(p_7 \oplus k_7) \oplus s(k_{13}) \oplus k_0 \oplus k_4 \oplus k_8 \oplus 1

x_9^1 = s(p_8 \oplus k_8) \oplus 2s(p_{13} \oplus k_{13}) \oplus 3s(p_2 \oplus k_2) \oplus s(p_7 \oplus k_7) \oplus s(k_{14}) \oplus k_1 \oplus k_5 \oplus k_9

x_{10}^1 = 2s(p_8 \oplus k_8) \oplus 3s(p_{13} \oplus k_{13}) \oplus s(p_2 \oplus k_2) \oplus s(p_7 \oplus k_7) \oplus s(k_{15}) \oplus k_2 \oplus k_6 \oplus k_{10}

x_{11}^1 = 2s(p_8 \oplus k_8) \oplus 3s(p_{13} \oplus k_{13}) \oplus s(p_2 \oplus k_2) \oplus s(p_7 \oplus k_7) \oplus s(k_{12}) \oplus k_3 \oplus k_7 \oplus k_{11}

x_{12}^1 = 2s(p_{12} \oplus k_{12}) \oplus 3s(p_1 \oplus k_1) \oplus s(p_6 \oplus k_6) \oplus s(p_{11} \oplus k_{11}) \oplus s(k_{13}) \oplus k_{12} \oplus k_0 \oplus k_4 \oplus k_8 \oplus 1

x_{13}^1 = s(p_{12} \oplus k_{12}) \oplus 2s(p_1 \oplus k_1) \oplus 3s(p_6 \oplus k_6) \oplus s(p_{11} \oplus k_{11}) \oplus s(k_{14}) \oplus k_{13} \oplus k_1 \oplus k_5 \oplus k_9

x_{14}^{1} = 2s(p_{12} \oplus k_{12}) \oplus 3s(p_{1} \oplus k_{1}) \oplus s(p_{6} \oplus k_{6}) \oplus s(p_{11} \oplus k_{11}) \oplus s(k_{15}) \oplus k_{14} \oplus k_{2} \oplus k_{6} \oplus k_{10}

x_{15}^1 = 2s(p_{12} \oplus k_{12}) \oplus 3s(p_1 \oplus k_1) \oplus s(p_6 \oplus k_6) \oplus s(p_{11} \oplus k_{11}) \oplus s(k_{12}) \oplus k_{15} \oplus k_3 \oplus k_7 \oplus k_{11}

(5.1)

```

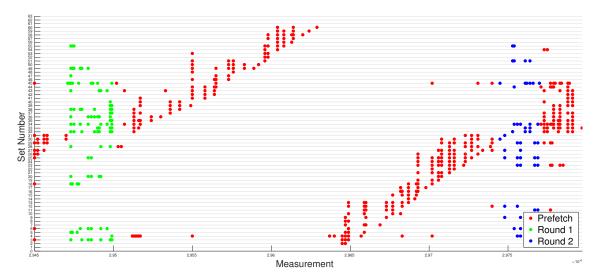

Figure 5.5: Memory footprint of the AES execution inside enclave over time steps. At each step, a few instructions has been executed.

Equations 5.1 show the relations of the first round key bytes.  $k_i$  is a key byte, and  $x_i^1$  is the index of each T-Table lookup in the second round. We first gather enough information for the high nibbles of the key bytes from the first round memory accesses. At the next step, solving the above equations using the information from the second round traces reduce the key space to a computationally small size. An experiment on a set of simulated data gathered using the binary instrumentation tool, Pin, shows that an ideal cache access trace of the first two AES rounds (32 memory accesses) reduce the key size to 4-8 bits.

In our specific practical attack, we face three problems:

- 1. Even in our high resolution attack, we have noise that adds false positives and negatives to our observed memory access patterns.

- 2. Our experiments show that the out-of-order execution and parallel processing of memory accesses does not allow for a full serialization of the observed memory accesses.

- 3. Separating memory accesses belonging to different rounds can be challenging.

The first two facts can be observed in Figure 5.5, which potentially shows 16 memory accesses to each round of a 4 T-table (4 access per table) AES. Due to our high resolution channel and the out-of-order execution of instructions, we observe that we interrupt the out-of-order execution pipeline while a future memory access is being fetched. Thus, interrupting the processor and evicting the entire L1D cache on each measurement forces the processor to repeatedly load the cache line memory until the target read instruction execution completes.

Hence, attributing observed accesses to actual memory accesses in the code is not trivial. Although this behavior adds some confusion, we show that observed

Figure 5.6: First round attack key recovery success rate.